ICs for Consumer Electronics

Confidential

Preliminary

User's Manual

TVTEXT PRO SDA 55xx

Version 1.21 July 99

| TVTEXT PRO<br>Revision History: |           | User's Manual Version 1.21 July 99        |  |

|---------------------------------|-----------|-------------------------------------------|--|

| Previous                        | Releases: | Version 1.1 Dec. 98, Version 1.2 April 99 |  |

| Page                            | Subjects  |                                           |  |

|                                 | See Chap  | oter List of Changes.                     |  |

|                                 |           |                                           |  |

|                                 |           |                                           |  |

#### Edition July 99

# Published by Infineon Technologies, Bereich Halbleiter, Marketing-Kommunikation Balanstraße 73, D-81541 München.

© Infneon Technologies 1999. All Rights Reserved.

As far as patents or other rights of third parties are concerned, liability is only assumed for components per se, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Offices of Infineon Technologies in Germany or Infineon Technologies Companies and Representatives worldwide.

Due to technical requirements components may contain dangerous substances. For information on the type in question please contact your nearest Infineon Technolgies Office.

| 1<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6                                           | Overview Preface Organization of this document Related Documentation Introduction Features Logic Symbol Block diagram                                                                                                                                                | 9<br>10<br>11<br>12                                |

|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 2<br>2.1<br>2.2<br>2.3                                                                | Package and Pinning                                                                                                                                                                                                                                                  |                                                    |

| 3<br>3.1                                                                              | SFR Overview                                                                                                                                                                                                                                                         |                                                    |

| 4<br>4.1<br>4.2                                                                       | Clock System General Function Register Description                                                                                                                                                                                                                   | 33                                                 |

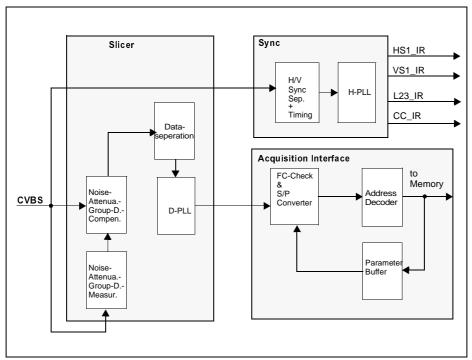

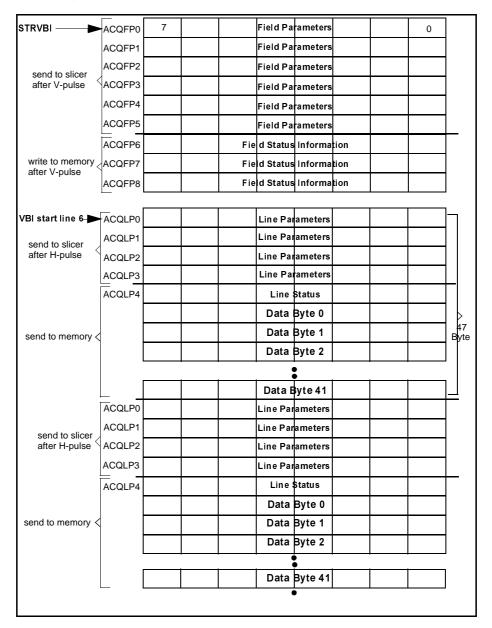

| 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.3<br>5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.5<br>5.5.1 | Slicer and Acquisition General Function Slicer Architecture Distortion Processing Data Separation H/V-Synchronization Acquisition Interface FC-Check Interrupts VBI Buffer and Memory Organization Register Description RAM Registers Recommended Parameter Settings | 39<br>40<br>41<br>42<br>42<br>43<br>43<br>46<br>48 |

| 6<br>6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.2<br>6.3<br>6.3.1                            | Microcontroller  Architecture  CPU-Hardware  CPU Timing  Addressing Modes  Ports and I/O-Pins Instruction Set  Notes on Data Addressing Modes                                                                                                                        | 69<br>63<br>63<br>65                               |

| 6.3.2<br>6.3.3                                                                        | Notes on Program Addressing Modes                                                                                                                                                                                                                                    | 68                                                 |

| 6.3.4                                                                                        | Instruction Opcodes in Hexadecimal Order                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

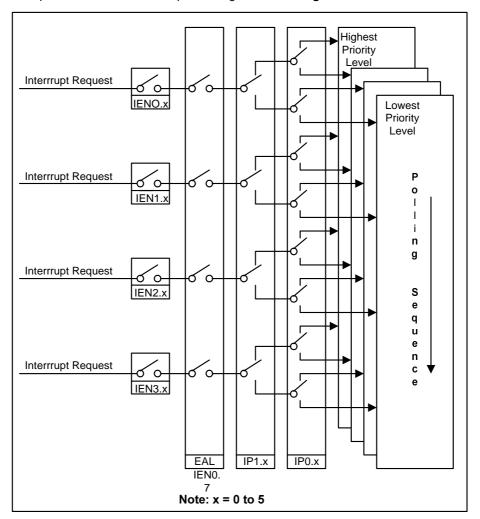

| 7 7.1 7.2 7.3 7.4 7.4.1 7.5 7.6 7.6.1 7.7 7.8 7.9 7.10 7.11 7.12 7.13 7.14 7.15 7.16         | Interrupts         83           Interrupt System         83           Interrupt Sources         83           Overview         84           Enabling interrupts         85           Interrupt Enable registers (IE0 IE1 IE2 IE3)         85           Interrupt source registers         87           Interrupt priority         90           Interrupt Priority registers (IP0 IP1)         91           Interrupt Vectors         92           Interrupt and memory extension         93           Interrupt Handling         93           Interrupt Latency         94           Interrupt Flag Clear         94           Interrupt return         94           Interrupt Nesting         94           External Interrupts         95           Extension of Standard 8051 Interrupt Logic         95           Interrupt Task Function         97 |

| 8<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5                                                         | Power Saving modes         99           Power Save mode registers         99           Idle mode         103           Power down mode         104           Power save mode         104           Slow down mode         104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9<br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>9.9<br>9.10<br>9.10.1<br>9.10.2 | Reset       105         Reset sources       105         Reset filtering       105         Reset duration       105         Registers       105         Functional blocks       105         RAMs       105         Analog blocks       106         Processor       106         Ports       106         Initialization phase       106         Acquisition       106         Display       106                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 10<br>10.1                                                                                   | Memory Organization107Program Memory107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

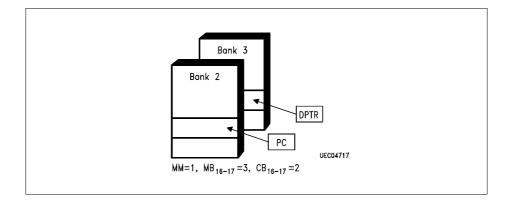

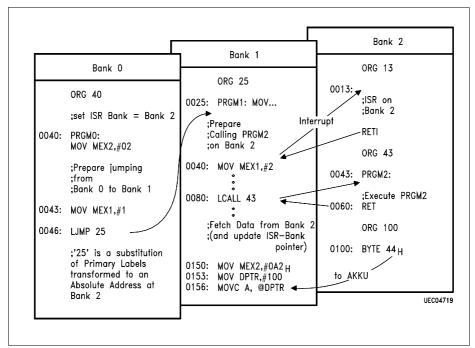

| 0.2<br>0.2.1<br>0.2.2<br>0.3<br>0.3.1<br>0.3.2<br>0.3.3<br>0.3.4<br>0.3.5<br>0.3.6<br>0.3.7<br>0.3.8<br>0.3.9<br>0.3.10 | Internal Data RAM  CPU RAM  Extended Data RAM(XRAM)  Memory Extension  Memory extension registers  Reset value  Program memory Banking (LJMP)  CALLs and Interrupts  Stack Full  Timing  Interfacing Extended memory  Interfacing Extended stack  Application Examples  ROM and ROMless version. | 108109110112113113114114        |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 1<br>1.1<br>1.2                                                                                                         | Wodes Multiprocessor Communication                                                                                                                                                                                                                                                               | 117                             |

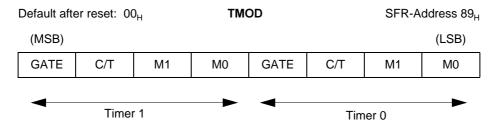

| 2<br>2.1<br>2.1.1<br>2.1.2<br>2.1.3                                                                                     | General Purpose Timers/Counters  Timer/Counter 0: Mode Selection  Configuring the Timer/Counter Input  Timer/Counter Mode Register  Timer/Counter Control Register                                                                                                                               | 121                             |

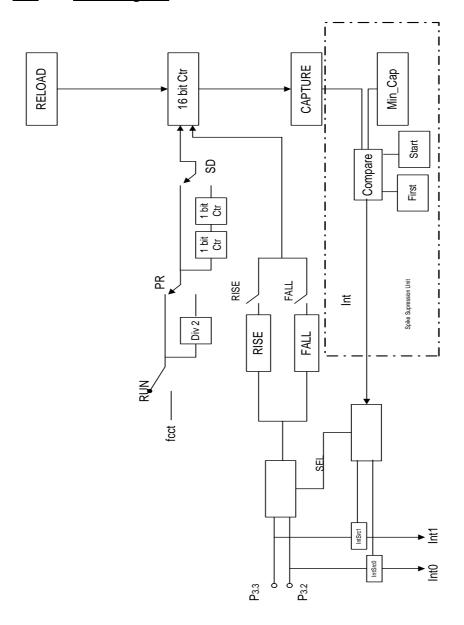

| 3<br>3.1<br>3.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7                                   | Capture reload timer Input clock Reset values Functional description Port pin Slow down mode Run Overflow Modes Normal Capture mode Polling mode                                                                                                                                                 |                                 |

| 3.3.8<br>3.3.9<br>3.3.10<br>3.3.11<br>3.3.12<br>3.4<br>3.5                                                              | Capture mode with spike suppression at the start of a telegram . First event                                                                                                                                                                                                                     | 127<br>127<br>128<br>128<br>128 |

| 3.6                                                                                                                     | Time resolution                                                                                                                                                                                                                                                                                  | 131                             |

| 13.7                                                                                 | Block diagram                                                                                                                                                                                                                        | 132                                                         |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

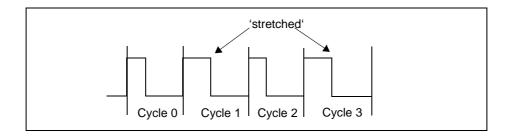

| 14<br>14.1<br>14.2<br>14.3<br>14.4<br>14.4.1<br>14.4.2<br>14.5<br>14.6<br>14.7       | Pulse Width Modulation Unit  Reset Values Input clock Port pins Functional description 8 bit PWM 14 bit PWM  Cycle time Power down, idle and Power save mode. Timer Control registers                                                | 133<br>133<br>134<br>134<br>135<br>136<br>136               |

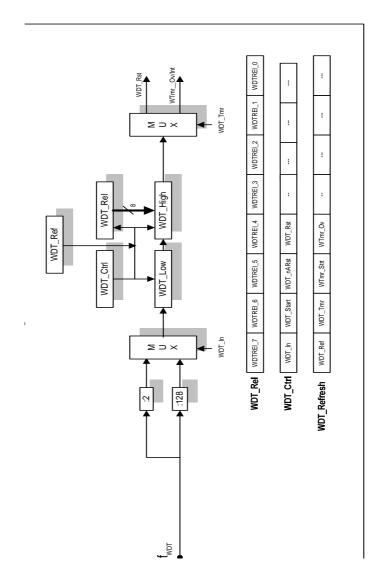

| 15.1<br>15.1<br>15.2<br>15.3<br>15.4<br>15.5<br>15.6<br>15.7                         | Watchdog Timer Input clock Starting WDT Refresh WDT reset Power down mode Time period Block Diagram WDT as general purpose timer.                                                                                                    | 141<br>141<br>142<br>142<br>143<br>144                      |

| 16<br>16.1<br>16.2                                                                   | Analog Digital Converter (CADC)  Power Down and Wake Up  Register Description                                                                                                                                                        | 147                                                         |

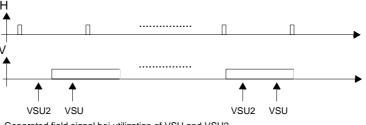

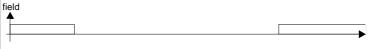

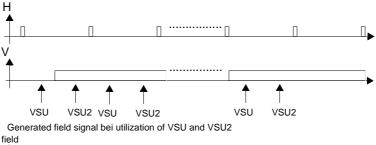

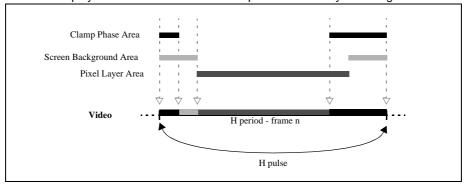

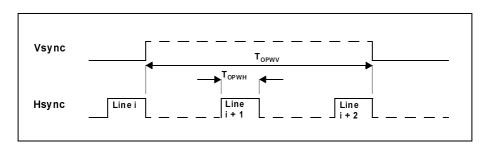

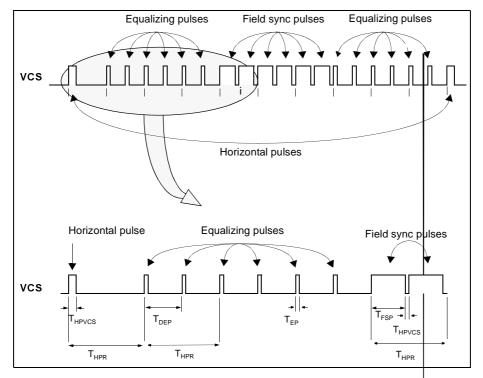

| 17<br>17.1<br>17.1.1<br>17.1.2<br>17.2                                               | Sync System General Description Screen Resolution. Sync Interrupts Register Description                                                                                                                                              | 153<br>153<br>155                                           |

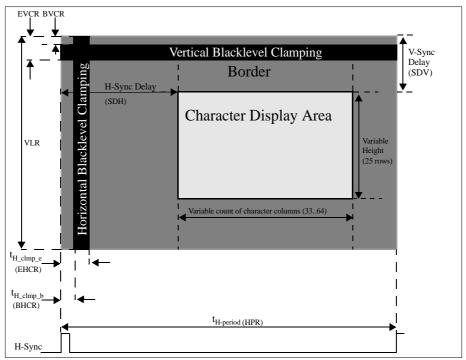

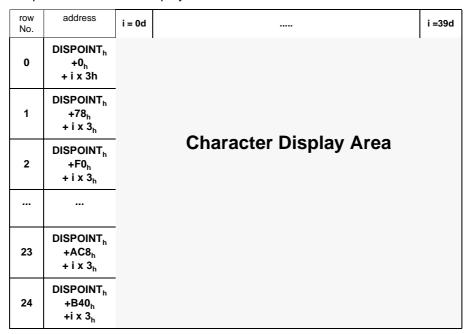

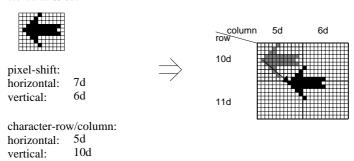

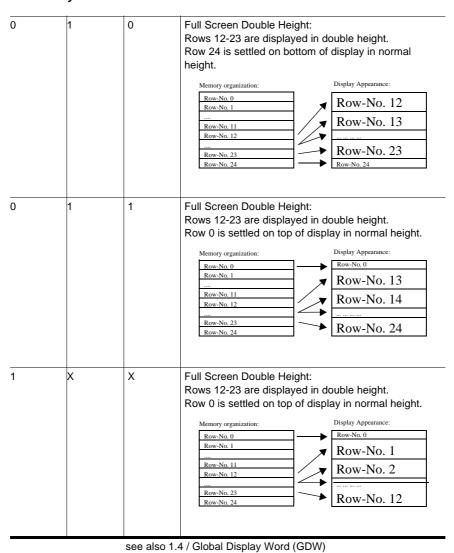

| 18<br>18.1<br>18.2<br>18.3<br>18.3.1<br>18.3.2<br>18.3.3<br>18.3.4<br>18.4<br>18.4.1 | Display Display Features Display Memory Parallel Character Attributes Access of Characters Flash Character Individual Double Height Character Individual Double Width Global OSD Attributes Character Display Area Resolution Cursor | 170<br>171<br>172<br>173<br>176<br>176<br>178<br>179<br>183 |

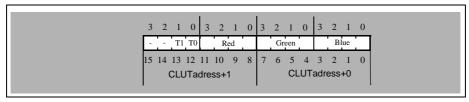

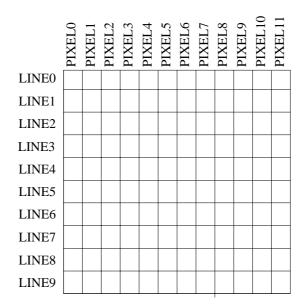

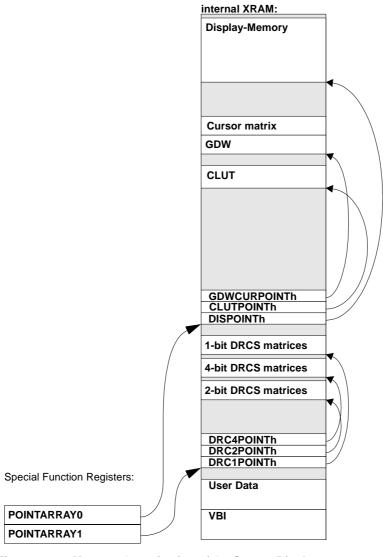

| 18.4.3<br>18.4.4<br>18.4.5<br>18.4.6<br>18.4.7<br>18.4.8<br>18.4.9<br>18.4.10<br>18.5<br>18.6.1<br>18.6.2<br>18.6.3<br>18.6.4<br>18.6.5 | Border Color         187           Full Screen Double Height         188           Flash Rate Control         190           Transparency of Boxes         191           CLUT         194           Character Resolution         199           Shadowing         201           Progressive Scan         202           DRCS characters         203           Memory Organization of DRCS characters         203           Memory Organization         206           Character Display Area         208           CLUT Area         208           Global Display Word/Cursor         208           1-bit/2-bit/4-bit DRCS character         209           Overview on the SFR registers         210 |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19<br>19.1                                                                                                                              | D/A Converter.211Register Description.211                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 20<br>20.1<br>20.2<br>20.3<br>20.4<br>20.5                                                                                              | Electrical Characteristics         215           Absolute Maximum Ratings         215           Operating Range         215           DC Characteristics         215           Timings         221           Package Outlines         224                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 21                                                                                                                                      | <b>Glossary</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 22                                                                                                                                      | Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 23                                                                                                                                      | List of changes since last edition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

8

Overview

#### 1 Overview

#### 1.1 Preface

TVText Pro is a 8-bit controller based on SIEMENS Enhanced 8051 core with embedded teletext, On screen Display and TV controller functions. TVText Pro can be used for a wide range of TV and OSD applications. This document provides complete reference information of the TVText Pro system.

#### 1.2 Organization of this document

· Chapter 1, Overview

Gives a general description of the product and lists the key features.

Chapter 2, Package and Pinning

Lists pin locations with associated signals, categorizes signals according to function, and describes signals.

· Chapter 3, SFR Overview

List of the registers.

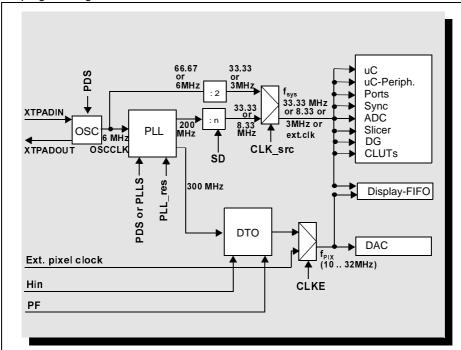

• Chapter 4, Clock System

Describes Clock system and it's distribution

• Chapter 5, Slicer and Acquisition

Describes slicer and acquisiton interface

• Chapter 6, Microcontroller

Describes microcontroller, instruction set, ports

• Chapter 7, Interrupts

Describes interrupts, priorities, sources, enhancements to standard 8051 interrupt logic.

• Chapter 8, Power Saving modes

Describes the four power saving modes of the device.

• Chapter 9, Reset

Describes reset requirements and behavior of the device

• Chapter 10, Memory Organization

Describes internal/external RAM, ROM and Memory extension

Chapter 11, UART

Describes peripheral UART

• Chapter 12, General Purpose Timers/Counters

Describes peripherals Timer0 and timer 1

Overview

• Chapter 13, Capture reload timer

Describes peripheral CRT

• Chapter 14, Pulse Width Modulation Unit

Describes peripheral PWM

• Chapter 15, Watchdog Timer

Describes peripheral Watchdog timer

• Chapter 16, Analog to Digital converter

Describes ADC functionality.

• Chapter 17, Sync System

Screen resolution, sync mechanism

• Chapter 18, Display

Display features, modes and their usage

· Chapter 19, Digital to Anaog converter

Describes DAC operation

• Chapter 20, Electrical Characteristics

Lists all important AC and DC Values and the maximum operating conditions of SDA55xx.

• Chapter 21,22 &23 Glossary, Index and List of changes since last edition

Provides a list of used terms and abbreviations, their explanation and where to find them in that document and changes since last edition

#### 1.3 Related Documentation

For easier understanding of this specification it is recommended to read the documentation listed in the following table.

| Document Name | Document Purpose |

|---------------|------------------|

|               |                  |

|               |                  |

Overview

#### 1.4 Introduction

The SDA 55xx is a single chip teletext decoder for decoding World System Teletext data as well as Video Programming System (VPS), Program Delivery Control (PDC), and Wide Screen Signalling (WSS) data used for PAL plus transmissions (line 23).

The device provides an integrated general-purpose, fully 8051-compatible Microcontroller with television specific hardware features. Microcontroller has been enhanced to provide powerful features such as memory banking, data pointers and additional interrupts etc.

The on-chip display unit for displaying Level 1.5 teletext data can also be used for customer defined on-screen displays.

Internal XRAM consists of up to 16 KBytes. Device has an internal ROM of up to 128 KBytes. ROMless versions can access up to 1MByte of external RAM and ROM.

The SDA 55xx supports a wide range of standards including PAL, NTSC and contains a digital slicer for VPS, WSS, PDC, and TTX, an accelerating acquisition hardware module, a display generator for Level 1.5 TTX data and powerful On screen Display capabilities based on parallel attributes, and Pixel oriented characters (DRCS)

The 8 bit Microcontroller runs at 360 ns. cycle time (min.). Controller with dedicated hardware does most of the internal TTX acquisition processing, transfers data to/from the external memory interface and receives/transmits data via I<sup>2</sup>C-firmware user-interface.

The slicer combined with dedicated hardware stores TTX data in a VBI buffer of 1 Kilobyte. The Microcontroller firmware performs all the acquisition tasks (hamming- and parity-checks, page search and evaluation of header control bits) once per field.

Additionally, the firmware can provide high-end Teletext-features like Packet-26-handling, FLOF, TOP and list-pages. The interface to the user software is optimized for minimal overhead.

SDA 55xx is realized in 0.25 micron technology with 2.5V supply voltage and 3.3V I/O (TTL compatible).

The software and hardware development environment (TEAM) is available to simplify and speed up the development of the software and On Screen Display. **TEAM** stands for: **TVT Expert Application Maker**. It improves the TV controller software quality in following aspects:

- · Shorter time to market

- Re-usability

- · Target independent development

- · Verification and validation before targeting

- General test concept

- Graphical interface design requiring minimum programming and controller know how

- Modular and open tool chain, configurable by customer

Overview

#### **CMOS**

#### 1.5 Features

#### General

- Feature selection via special function register

- Simultaneous reception of TTX, VPS, PDC, and WSS (line 23)

- Supply Voltage 2.5 and 3.3 V

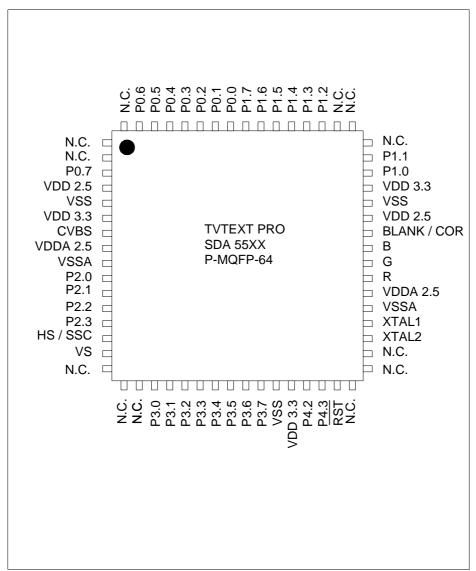

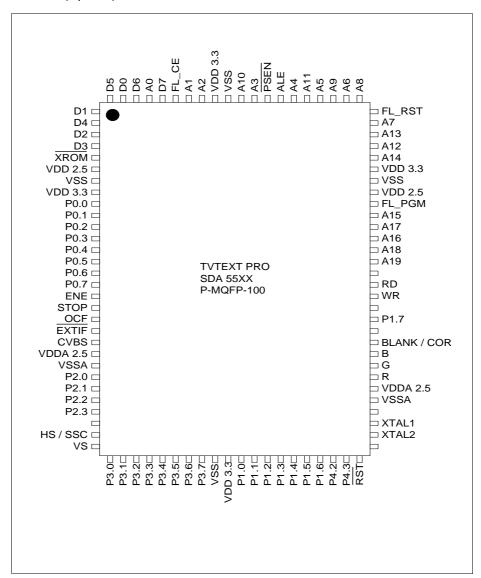

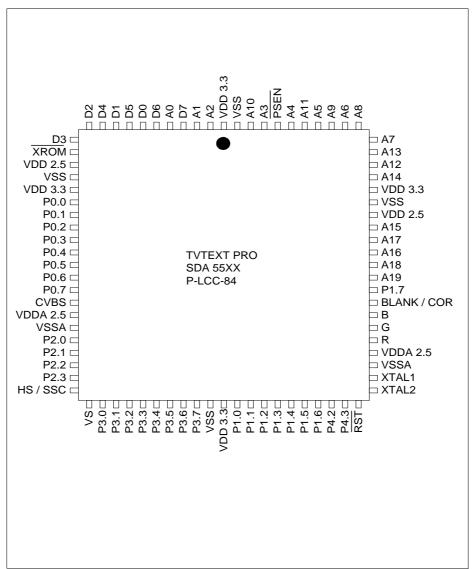

- ROM version package P-SDIP 52, P-MQFP64

- Romless version package P-MQFP100,P-LCC84

#### **External Crystal and Programmable clock speed**

- Single external 6MHz crystal, all necessary clocks are generated internally

- CPU clock speed selectable via special function registers.

- Normal Mode 33.33 Mhz CPU clock, Power Save mode 8.33 Mhz

# P-SDIP-52

#### **Microcontroller Features**

- 8bit 8051 instruction set compatible CPU.

- 33.33-MHz internal clock (max.)

- 0.360 µs (min.) instruction cycle

- Two 16-bit timers

- Watchdog timer

- · Capture compare timer for infrared remote control decoding

- Pulse width modulation unit (2 channels 14 bit, 6 channels 8 bit)

- ADC (4 channels, 8 bit)

- UART

| Туре                 | Package              |

|----------------------|----------------------|

| TVTEXT PRO (ROM)     | P-SDIP-52, P-MQFP-64 |

| TVTEXT PRO (ROMIess) | P-MQFP-100, P-LCC-84 |

Overview

#### Memory

- Non-multiplexed 8-bit data and 16 ... 20-bit address bus (ROMless Version)

- Memory banking up to 1Mbyte (Romless version)

- Up to 128 Kilobyte on Chip Program ROM

- Eight 16-bit data pointer registers (DPTR)

- · 256-bytes on-chip Processor Internal RAM (IRAM)

- 128bytes extended stack memory.

- Display RAM and TXT/VPS/PDC/WSS-Acquisition-Buffer directly accessible via MOVX

- UP to 16KByte on Chip Extended RAM(XRAM) consisting of;

- 1 Kilobyte on-chip ACQ-buffer-RAM (access via MOVX)

- 1 Kilobyte on-chip extended-RAM (XRAM, access via MOVX) for user software

- 3 Kilobyte Display Memory

#### **Display Features**

- ROM Character Set Supports all East and West European Languages in single device

- · Mosaic Graphic Character Set

- Parallel Display Attributes

- · Single/Double Width/Height of Characters

- · Variable Flash Rate

- Programmable Screen Size (25 Rows x 33...64 Columns)

- Flexible Character Matrixes (HxV) 12 x 9...16

- Up to 256 Dynamical Redefinable Characters in standard mode; 1024 Dynamical Redefinable Characters in Enhanced Mode

- CLUT with up to 4096 color combinations

- Up to 16 Colors per DRCS Character

- One out of Eight Colors for Foreground and Background Colors for 1-bit DRCS and ROM Characters

- Shadowing

- Contrast Reduction

- · Pixel by Pixel Shiftable Cursor With up to 4 Different Colors

- Support of Progressive Scan and 100 Hz.

- 3 X 4Bits RGB-DACs On-Chip

- Free Programmable Pixel Clock from 10 MHZ to 32MHz

- Pixel Clock Independent from CPU Clock

- Multinorm H/V-Display Synchronization in Master or Slave Mode

Overview

#### **Acquisition Features**

- Multistandard Digital Data Slicer

- Parallel Multi-norm Slicing (TTX, VPS, WSS, CC, G+)

- Four Different Framing Codes Available

- Data Caption only Limited by available Memory

- Programmable VBI-buffer

- · Full Channel Data Slicing Supported

- · Fully Digital Signal Processing

- Noise Measurement and Controlled Noise Compensation

- Attenuation Measurement and Compensation

- Group Delay Measurement and Compensation

- Exact Decoding of Echo Disturbed Signals

#### **Ports**

- One 8-bit I/O-port with open drain output and optional I<sup>2</sup>C Bus emulation suport(Port0)

- Two 8-bit multifunction I/O-ports (Port1, Port3)

- One 4-bit port working as digital or analog inputs for the ADC (Port2)

- One 2-bit I/O port with secondary functions (P4.2, 4.3, 4.7)

- One 4-bit I/O-port with secondary function (P4.0, 4.1, 4.4) (Not available in P-SDIP 52)

# Overview

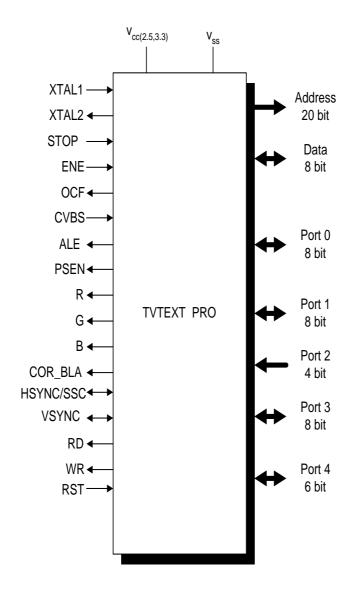

# 1.6 Logic Symbol

# Overview

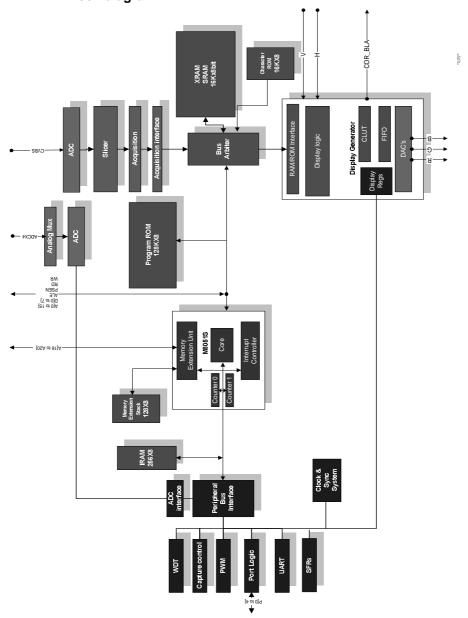

# 1.7 Block diagram

# Package and Pinning

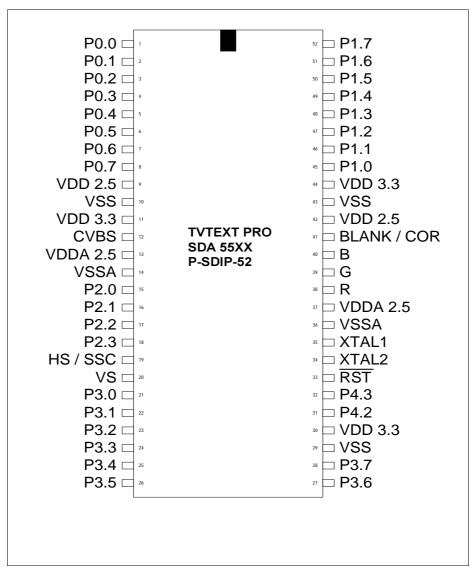

# 2 Package and Pinning

# 2.1 Pin Functions (ROM and ROMless Version)

| Symbol             | Fund                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | etion                                                                                                                                       |                                                |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| P0.0-P0.7          | Type<br>I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Additional reference                                                                                                                        | Available:<br>SDIP52,MQFP64,<br>MQFP100,PLCC84 |

|                    | have                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 is a 8-bit open drain bidirectional I/O-port.  1 written to them float; in this state they or impedance inputs (e.g. for software drort). | can be used as                                 |

| P1.0-P1.7          | Type<br>I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Additional reference                                                                                                                        | Available:<br>SDIP52,MQFP64,<br>MQFP100,PLCC84 |

| PWM                | Port 1 is a 8-bit bidirectional multifunction I/O port with internal pull-up resistors. Port 1 pins that have 1 written to them are pulled high by the internal pull-up resistors and in that state can be used as inputs.  The secondary functions of port 1 pins are:  Port bits P1.0 - P1.5 contain the 6 output channels of the 8-bit pulse width modulation unit.  Port bits P1.6 - P1.7 contain the two output channels of the 14-bit pulse width modulation unit. |                                                                                                                                             |                                                |

| P2.0-P2.3          | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Additional reference                                                                                                                        | Available:<br>SDIP52,MQFP64,<br>MQFP100,PLCC84 |

| ADC                | Port<br>Port                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2 is a 4-bit input port without pull-up resisto<br>2 also works as analog input for the 4-char                                              | ors.<br>nnel-ADC.                              |

| P3.0-P3.7          | Type<br>I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Additional reference                                                                                                                        | Available:<br>SDIP52,MQFP64,<br>MQFP100,PLCC84 |

| Alternate function | Port 3 is an 8-bit bidirectional I/O port with internal pull-up resistors. Port 3 pins that have 1 written to them are pulled high by the internal pull-up resistors and in that state can be used as inputs.  To use the secondary functions of Port 3, the corresponding output latch must be programmed to a one (1) for that function to operate. The secondary functions are as follows:  P3.0: ODD/EVEN indicate output.                                           |                                                                                                                                             |                                                |

| Alternate function | P3.1: external extra interrupt 0 (INTX0)/UART(TXD) P3.2: interrupt 0 input/timer 0 gate control input (INT0) P3.3: interrupt 1 input/timer 1 gate control input (INT1) P3.4: counter 0 input (T0) P3.5: counter 1 input (T1) or In master mode HS or VCS ou P3.7 external extra interrupt 0 (INTX1)/UART(RXD)                                                                                                                                                            |                                                                                                                                             | (INT0)<br>(INT1)<br>or VCS output.             |

# Package and Pinning

| Symbol                                                                              | Func                                                                                                            | etion                                                                                                                                                                                                                             |                                                |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| P4.2,P4.3, P4.7                                                                     | Type<br>I/O                                                                                                     | Additional reference                                                                                                                                                                                                              | Available:<br>SDIP52,MQFP64,<br>MQFP100,PLCC84 |

|                                                                                     | Port<br>interr<br>Seco<br>P4.2                                                                                  | 4 is a bidirectional I/O port with internal p 4 pins that have 1 written to them are pul hal pull-up resistors and in that state can be endary functions: RD, Read line. This signal is same as the D available in some packages. | led high by the used as inputs.                |

|                                                                                     | P4.3: WR, write line. This signal is same as the output of the pir WR, which is only available in some package. |                                                                                                                                                                                                                                   |                                                |

|                                                                                     | P4.7                                                                                                            | : VS, Vertical sync: ODD/Even, Odd/even f                                                                                                                                                                                         | ield indicator.                                |

| RST                                                                                 | Type                                                                                                            | Additional reference                                                                                                                                                                                                              | Available:<br>SDIP52,MQFP64,<br>MQFP100,PLCC84 |

|                                                                                     | resis                                                                                                           | we level on this pin resets the device. An tor permits power-on reset using only citor connected to $V_{\mbox{\scriptsize SS}}.$                                                                                                  | internal pull-up<br>one external               |

| $\mathbf{V}_{	extsf{DD3.3}} \ \mathbf{V}_{	extsf{DD2.5}} \ \mathbf{V}_{	extsf{SS}}$ | Type<br>PS                                                                                                      | Additional reference                                                                                                                                                                                                              | Available:<br>SDIP52,MQFP64,<br>MQFP100,PLCC84 |

|                                                                                     | $\begin{matrix} V_{\text{DD3.3}} \\ V_{\text{DD2.5}} \\ V_{\text{ss}} \end{matrix}$                             | Input/output (3.3V)<br>Supply voltage (2.5V)<br>Ground (0 V)                                                                                                                                                                      |                                                |

| $V_{\scriptscriptstyle \sf DDA}V_{\scriptscriptstyle \sf SSA}$                      | Type<br>PS                                                                                                      | Additional reference                                                                                                                                                                                                              | Available:<br>SDIP52,MQFP64,<br>MQFP100,PLCC84 |

|                                                                                     |                                                                                                                 | bly voltage for analog components.<br>nd for analog components.                                                                                                                                                                   |                                                |

| CVBS                                                                                | Туре                                                                                                            | Additional reference                                                                                                                                                                                                              | Available:<br>SDIP52,MQFP64,<br>MQFP100,PLCC84 |

|                                                                                     | CVB                                                                                                             | S input for the acquisition circuit.                                                                                                                                                                                              |                                                |

| HS/SC                                                                               | Type<br>I                                                                                                       | Additional reference                                                                                                                                                                                                              | Available:<br>SDIP52,MQFP64,<br>MQFP100,PLCC84 |

|                                                                                     | In sla                                                                                                          | ave mode Horizontal sync input or sand<br>ay synchronization.In master mode HS or                                                                                                                                                 | castle input for /CS output.                   |

| XTAL1                                                                               | Type<br>I                                                                                                       | Additional reference                                                                                                                                                                                                              | Available:<br>SDIP52,MQFP64,<br>MQFP100,PLCC84 |

|                                                                                     | Input                                                                                                           | of the inverting oscillator amplifier.                                                                                                                                                                                            |                                                |

# Package and Pinning

| Symbol  | Fund                                                                                                                                                                                 | Function                                  |                                                |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------|--|

| XTAL2   | Type<br>O                                                                                                                                                                            | Additional reference                      | Available:<br>SDIP52,MQFP64,<br>MQFP100,PLCC84 |  |

|         | Outp                                                                                                                                                                                 | ut of the inverting oscillator amplifier. |                                                |  |

| VS/P4.7 | Type<br>I/O                                                                                                                                                                          | Additional reference                      | Available:<br>SDIP52,MQFP64,<br>MQFP100,PLCC84 |  |

|         | Vertical sync input/output for display synchronization. Can also be used as digital input P4.7. Furthermore this pin can be selected as an ODD/EVEN indicator alternatively to P3.0. |                                           |                                                |  |

| R,G,B   | Type<br>O                                                                                                                                                                            | Additional reference                      | Available:<br>SDIP52,MQFP64,<br>MQFP100,PLCC84 |  |

|         | Red,                                                                                                                                                                                 | Green, Blue                               |                                                |  |

| COR_BLA | Type<br>O                                                                                                                                                                            | Additional reference                      | Available:<br>SDIP52,MQFP64,<br>MQFP100,PLCC84 |  |

|         | Cont                                                                                                                                                                                 | rast reduction and blanking               |                                                |  |

# Package and Pinning

# 2.2 Additional Pins or Functions for ROMless Version

| Symbol                      | Function                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                  |

|-----------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| A0-A16                      | Type<br>O                                           | Additional reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Available:<br>MQFP100,<br>PLCC84 |

|                             | Address bus for external program memory or data RAM |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                  |

| A17A19/<br>P4.0, P4.1, P4.4 | Type<br>I/O                                         | Additional reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Available:<br>MQFP100,<br>PLCC84 |

|                             | lines A<br>In por<br>intern<br>are pu               | power-on P4.0, P4.1, P4.4 work as addi A17A19. t mode, these port lines act as bidirection al pull-up resistors. Port pins that have '1' ulled high by the internal pull-up resistors are used as inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | al I/O port with written to them |

| D0-D7                       | Type<br>I/O                                         | Additional reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Available:<br>MQFP100,<br>PLCC84 |

|                             | Data bus for external memory or data RAM            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                  |

| STOP                        | Туре                                                | Additional reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Available:<br>MQFP100            |

|                             | bhase                                               | o<br>ation control line; Driving a low level du<br>e freezes the real time relevant internal pe<br>ners and interrupt controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ring the input<br>ripherals such |

| OCF                         | Type<br>O                                           | Additional reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Available:<br>MQFP100            |

|                             | Emula                                               | de Fetch<br>ation control line; A high level driven by<br>g output phase indicates the beginnir<br>ction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | the controller<br>ng of a new    |

| ENE                         | Туре                                                | Additional reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Available:<br>MQFP100            |

|                             | Only opera                                          | le Emulation<br>if this pin is set to zero externally, STOP<br>tional. ENE has an internal pull-up resistor in<br>the properties of the set o | which switches                   |

# Package and Pinning